NOR/NAND Flash 技术原理

基本单元

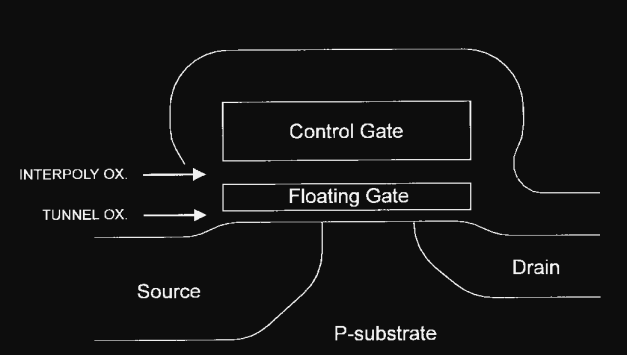

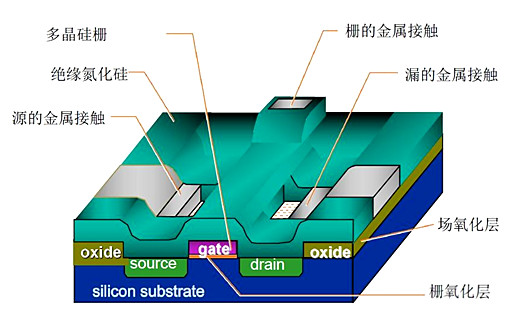

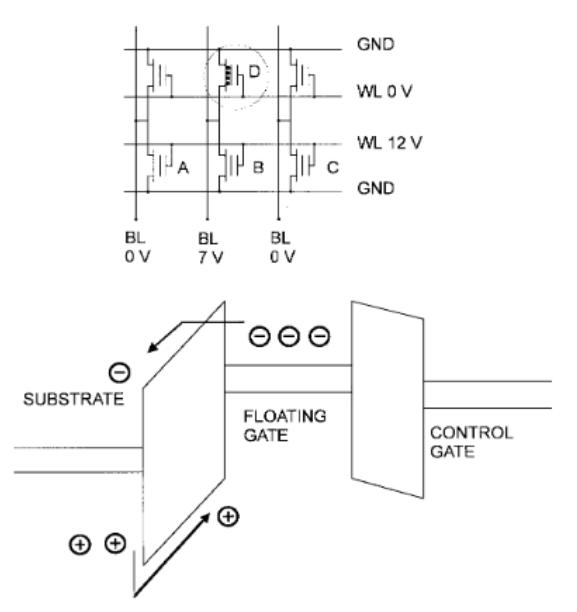

flash 的最基本的单元就是一个浮栅场效应管(Floating Gate FET),我们一般称其为一个 cell。

此处的“栅”应该读作 shān。

浮栅场效应管共有 4 个端电极,分别是为:

- 源极(Source):源极是电子(或空穴)的入口端。

- 漏极(Drain):漏极是电子(或空穴)的出口端。

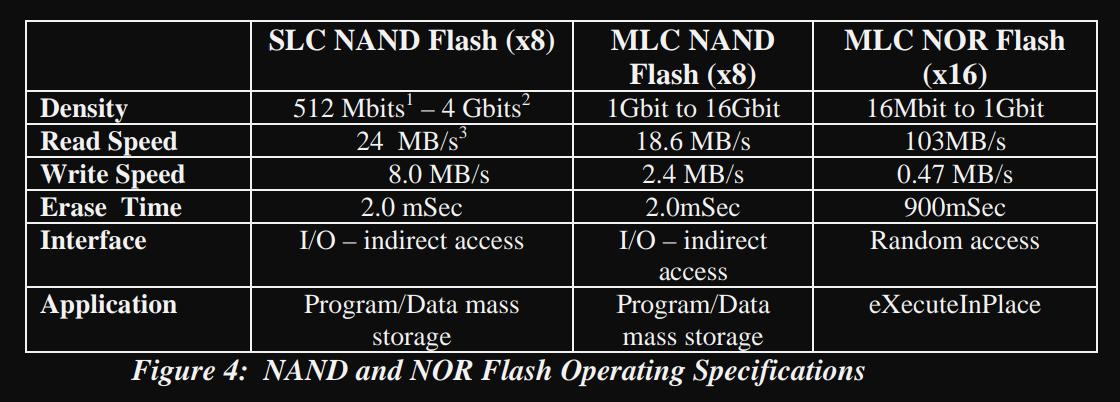

- 控制栅极(Control Gate):这是位于浮置栅极之上的另一个导电层,通过绝缘层与浮置栅极隔离。控制栅极是外部电压信号的施加点,它通过电场影响浮置栅极和通道的行为。

- 浮置栅极(Floating Gate):这是一个完全被绝缘层(如二氧化硅)包裹的导电层(通常是多晶硅)。由于被绝缘层包围,浮置栅极中的电荷无法直接泄漏,因此可以长期保持存储状态。

在场效应晶体管(FET,field effect transistor)中,主要有三个电极:

- 源极(Source):电子(或空穴)的入口端。

- 漏极(Drain): 电子(或空穴)的出口端。

- 栅极(Gate):控制电流在源极和漏极之间的流动。类似于一个开关,通过施加电压来调节晶体管的导通与关断。栅极通常位于导电通道的上方,并且通过绝缘层(如二氧化硅)与通道隔离开。

栅极的长度(即栅极在源极与漏极之间的距离)通常被用来定义集成电路的技术节点(如 7nm 工艺中的 7nm 指的是栅极长度)。栅极长度越小,晶体管可以实现的开关速度越快,但制造难度也越大。

基本单元操作原理

编程(写入)

目的:在浮置栅极中注入电子,改变其电荷状态,从而改变该存储单元的阈值电压,使其表示不同的逻辑状态(如“0”或“1”)。

过程:

- 高电压施加:在编程过程中,控制栅极上施加较高的电压。(需要内部升压电路或外部高压输入)

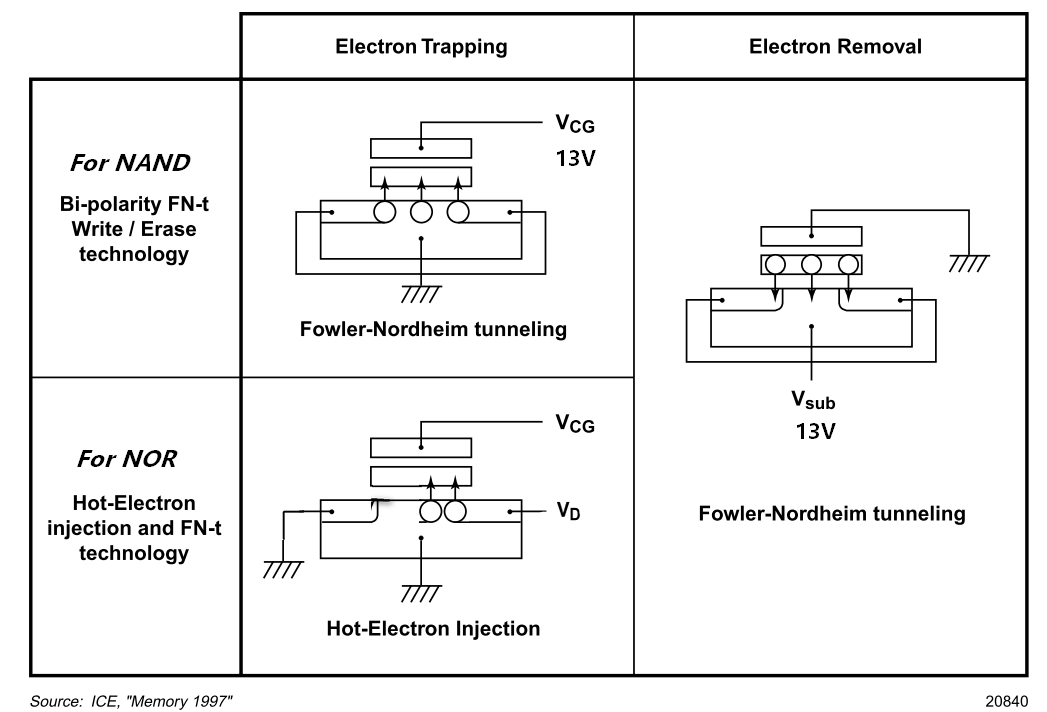

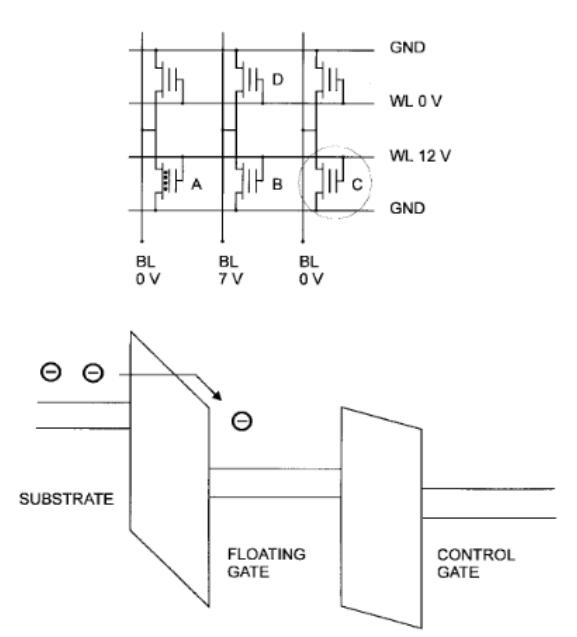

- F-N 隧道效应(Fowler Nordheim tunneling):主要用于 NAND flash 和现代 NOR flash,源极和漏极都接地,在电场的作用下,大量电子冲向绝缘层,部分电子通过量子隧穿效应穿过绝缘层,从源极或漏极注入浮置栅极(对于同一条 word line 上的其他 cell 如果不想进行编程操作,需要为位线施加电压,防止隧穿效应)。

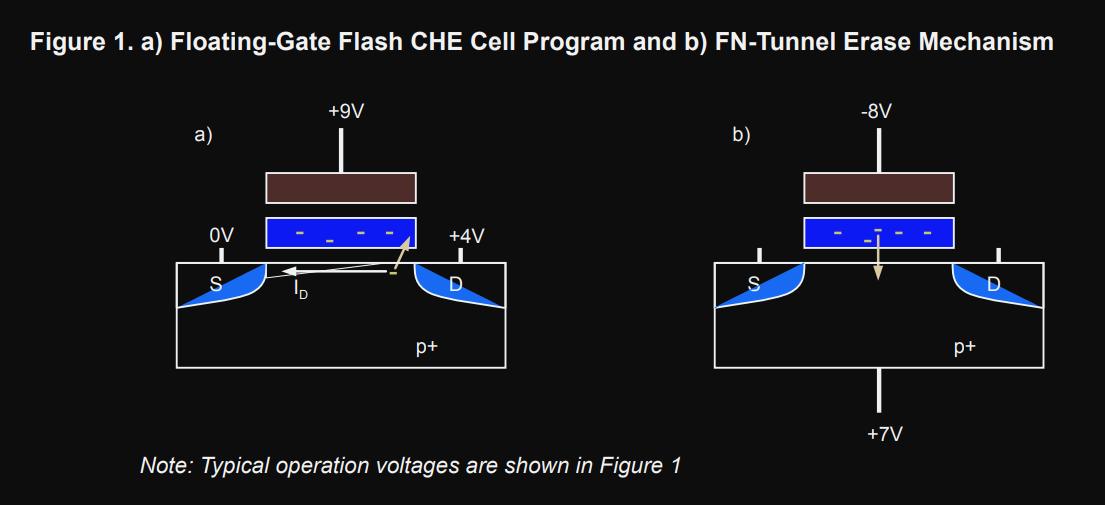

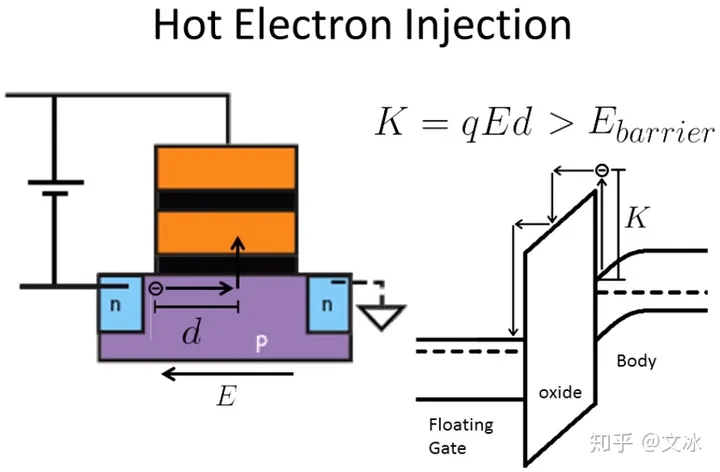

- 热电子注入(Hot Electron Injection):主要用于 EEPROM 和早期的 NOR flash,在漏极和源极间增加一个电压,源极一般接地,这时电子从源极流向漏极,且会产生加速,在到达漏极附近时达到最高速度,这就是热电子(高能粒子),加上控制栅极上的电压产生的垂直方向的电场,电子的轨迹会向上偏移,凭借其能量穿透绝缘层进入浮置栅极。

- 电荷存储:电子进入浮置栅极后被困住,因为浮置栅极完全被绝缘层包围,这些电荷会改变浮置栅极的电势。

一旦电子注入到浮栅上后,即便我们不再对存储器进行擦除、写入过程,电子仍然可能会慢慢逃逸出去(氧化层存在缺陷,且浮栅上的电子化学势比较高,电子倾向于离开浮栅)

读取

目的:检测浮置栅极的电荷状态,进而确定存储单元表示的逻辑值。

过程:

- 低电压施加:在读取操作时,控制栅极上施加一个较低的电压(该电压不足以引发量子隧穿效应)。

- 通道导通判断:根据浮置栅极中电荷的多少,存储单元的阈值电压(能够引起源漏导通的最低控制栅极电压)会不同。如果浮置栅极中有足够多的电子,则控制栅极上的电压将会被电子的负电荷抵消,不足以打开通道,导致存储单元处于“关断”状态(即不导通),表示一个逻辑值(如“0”)。如果浮置栅极中电荷较少或没有电荷,则控制栅极的电压足以打开通道,存储单元导通,表示另一个逻辑值(如“1”)。通过尝试不同的电压值,可以判断出浮置栅极中的电子数量(多比特存储单元需要尝试的次数更多)。

擦除

目的:将浮置栅极中的电子移除,恢复存储单元的初始状态(通常对应于逻辑“1”)。

过程:

- 反向电场:在擦除过程中,通常对源极(漏极/沟道)施加较高的正电压,控制栅极施加负电压(称为 negative gate erasure,或不施加电压)。这形成了一个反向电场。

- 电子移除:在电场的作用下,浮置栅极中的电子通过隧穿效应被拉回到源极或漏极,从而清空浮置栅极中的电荷。

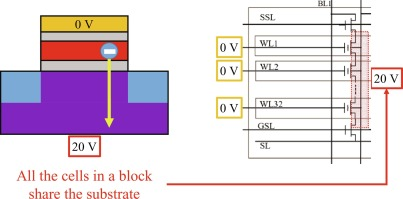

为什么要按照 block 擦除,而不是 page 或字节:

一种擦除电路的设计方式是在沟道上施加正向电压,这个过程如果以 block 为单位可以大大简化电路设计:

还有一种方式是 1988 年 Intel 提出的非对称源漏极设计,此时擦除是对源极施加正向电压,向控制栅极施加负电压,漏极悬空(只要将一个 block 的源极都连接到一个线路上即可,电路占用空间就能变小,这是提高 flash 容量的一种方式):

量子隧穿效应

经典物理学认为,物体越过势垒,有一定的阈值能量;所以,粒子能量小于此阈值能量的不能越过,能量大于此阈值能量的可以越过。举例来说,我们骑自行车过坡道,如果先用力骑,因此有一定初始能量,坡道不高的话,即使不蹬自行车也可以依靠惯性过去;但是,如果坡道很高,不蹬自行车,可能车上升到了一半,可能就退回来了。

而量子力学则认为,即便是粒子能量小于阈值能量,同时很多粒子冲向势垒,虽然也有一部分粒子会反弹,但是还会有一些粒子可以越过去,好像有一个隧道,因此称为量子隧道。

多比特存储单元

最早的 flash 设计中,一个 cell 用于保存一个 bit 的数据。

但后来人们发现一个 cell 中的电子的数量可以用用于表示更多的信息,比如将电子数量分为无(00)、少(01)、中(10)、多(11)四种状态就能表示 2 bit 信息。

也就有了 SLC(1bit)、MLC(2bit)、TLC(3bit)、QLC(4bit)技术。

优点

- 提高存储密度:多比特存储单元技术允许在相同物理空间中存储更多的数据,提高了存储密度。

- 降低成本:每个存储单元能够存储更多的数据,减少了每 GB 存储的成本。

缺点

- 耐久性降低:多比特存储单元的每个单元存储的电荷状态更多,导致擦写次数减少,耐久性相对较低。

- 读取和编程速度:读取和编程操作可能比单比特存储单元更慢,因为需要更精确地检测电荷状态。

- 错误率增加:随着存储状态的增加,错误率(如比特翻转)也会增加,通常需要更复杂的纠错技术。

NOR FLASH 和 NAND FLASH 的结构和特性

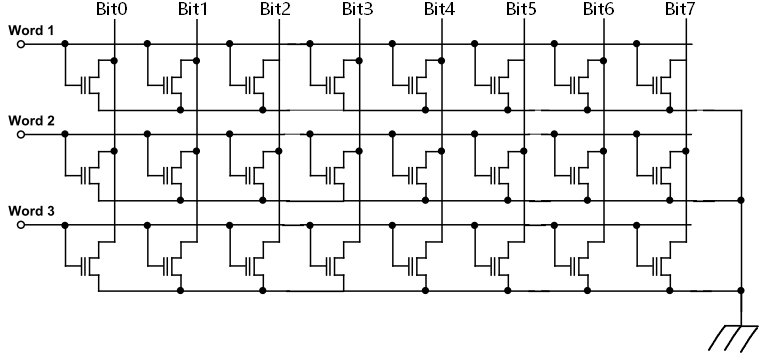

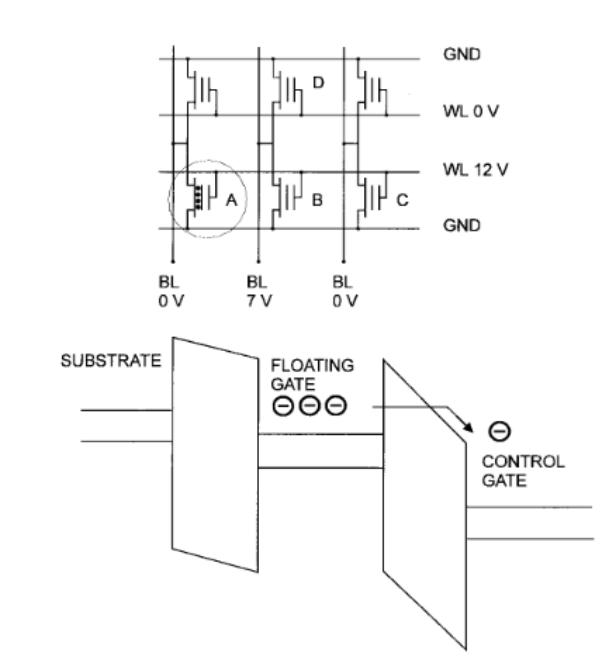

word line 是字线,每条 word line 将一组 cell 的控制栅极连接。

bit line 是位线,每条位线对一组 word 中的一个 cell 进行控制(一个 word 有几个 cell,就有几条 bit line 与之连接),多个 word 会共享一组 bit line。

这就意味着共享 bit line 的这些 word 只能串行访问(因为 bit line 是共享的资源,同一时间只能给一个 word 用),一般我们将这些共享同一组 bit line 的 word 组成的存储空间称为一个 page,不同 page 的 bit line 不同,所以不同 page 间可以并行访问。

根据这些 cell 的连接方式不同,flash 一般被分为 NOR Flash 和 nand flash。

NOR FLASH 的中的 N 是 NOT,含义是 Floating Gate 中有电荷时,读出‘0’,无电荷时读出‘1’,是一种‘非’的逻辑;OR 的含义是同一个 Bit Line 下的各个基本存储单元是并联的,是一种‘或’的逻辑,这就是 NOR 的由来。

NAND FLASH 的中的 N 是 NOT,含义是 Floating Gate 中有电荷时,读出‘0’,无电荷时读出‘1’,是一种‘非’的逻辑;AND 的含义是同一个 Bit Line 下的各个基本存储单元是串联的,是一种‘与’的逻辑,这就是 NAND 的由来。

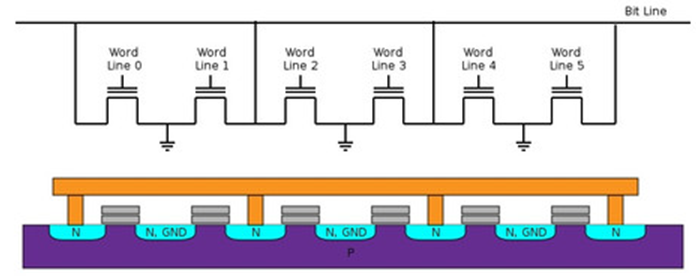

NOR FLASH

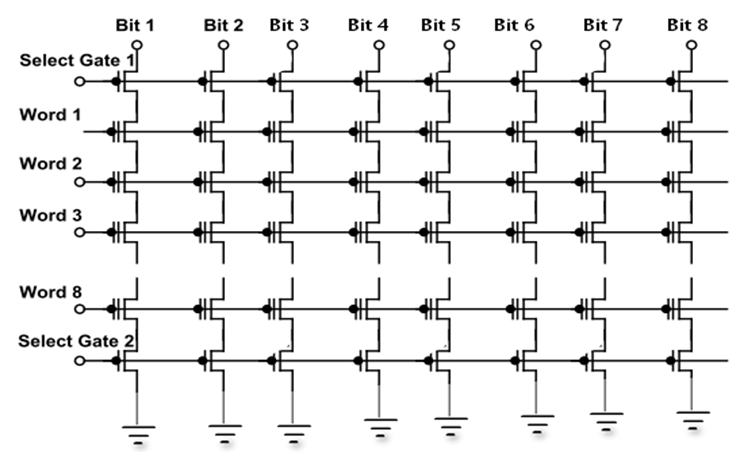

按本图所示,NOR FLASH 中,将源极接地。bit line 仅控制漏极,cell 之间为并联:

实际的硅切面图,每两个 word 共用一个地线,cell 间并联:

进行操作时,为相应的 word line 施加电压,然后对相应的 bit line 施加电压,可以实现单个 cell 的操作,在 SLC 下也就是位操作。因为是一个 word line 同时施加电压,一般操作(除了擦除)单位是一个 word(一般是一个字节)。

特性:

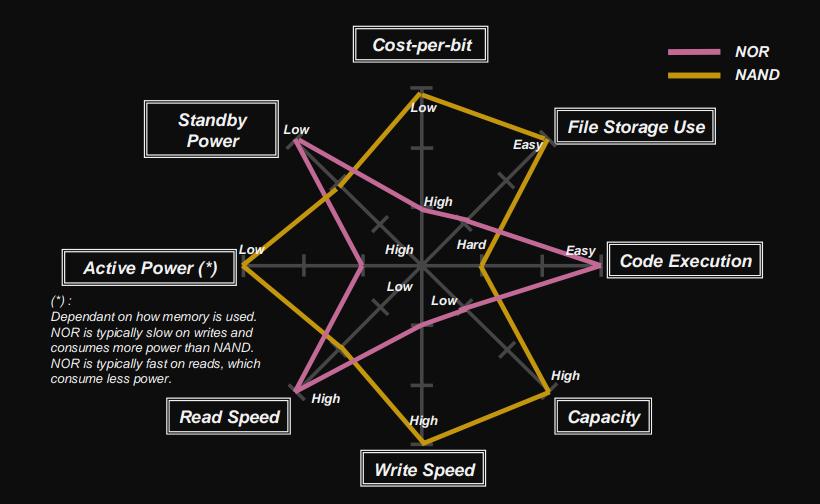

- 基本存储单元的并联结构决定了金属导线占用很大的面积,因此 NOR FLASH 的存储密度较低,无法适用于需要大容量存储的应用场合,即适用于 code-storage,不适用于 data-storage。

- 基本存储单元的并联结构决定了 NOR FLASH 具有存储单元可独立寻址且读取效率高的特性,因此适用于 code-storage,且程序可以直接在 NOR 中运行(即具有 RAM 的特性)。

- NOR FLASH 写入采用了热电子注入方式,效率较低,因此 NOR 写入速率较低,不适用于频繁擦除/写入场合。

NOR FLASH 接口

NOR Flash 按其接口分为:

- parallel NOR:并行 NOR

- serial NOR:串行 NOR,接口少,使用简单。主要是 SPI 接口的 NOR。

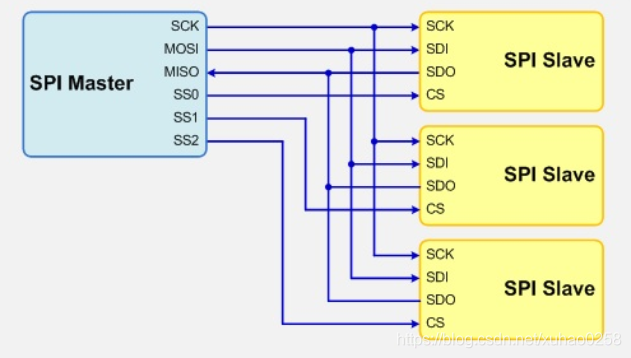

SPI 接口:

- SCK(Serial Clock):SCK 是串行时钟线,作用是 Master 向 Slave 传输时钟信号,控制数据交换的时机和速率;

- MOSI(Master Out Slave in):在 SPI Master 上也被称为 Tx-channel,作用是 SPI 主机给 SPI 从机发送数据;

- MISO(Master In Slave Out):在 SPI Master 上也被称为 Rx-channel,作用是 SPI 主机接收 SPI 从机传输过来的数据;

- CS/SS(Chip Select/Slave Select):作用是 SPI Master 选择与哪一个 SPI Slave 通信,低电平表示从机被选中(低电平有效);

SPI 分类:

标准 SPI 标准 SPI 通常就称 SPI,它是一种串行外设接口规范,有 4 根引脚信号:clk , cs, mosi, miso

Dual SPI 它只是针对 SPI Flash 而言,不是针对所有 SPI 外设。对于 SPI Flash,全双工并不常用,因此扩展了 mosi 和 miso 的用法,让它们工作在半双工,用以加倍数据传输。也就是对于 Dual SPI Flash,可以发送一个命令字节进入 dual mode,这样 mosi 变成 SIO0(serial io 0),mosi 变成 SIO1(serial io 1),这样一个时钟周期内就能传输 2 个 bit 数据,加倍了数据传输

Qual SPI 与 Dual SPI 类似,也是针对 SPI Flash,Qual SPI Flash 增加了两根 I/O 线(SIO2,SIO3),目的是一个时钟内传输 4 个 bit。所以对于 SPI Flash,有标准 spi flash,dual spi , qual spi 三种类型,分别对应 3-wire, 4-wire, 6-wire,在相同 clock 下,线数越多,传输速率越高。

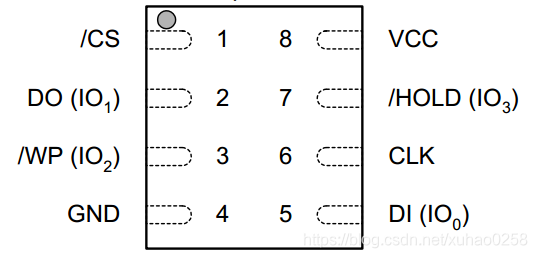

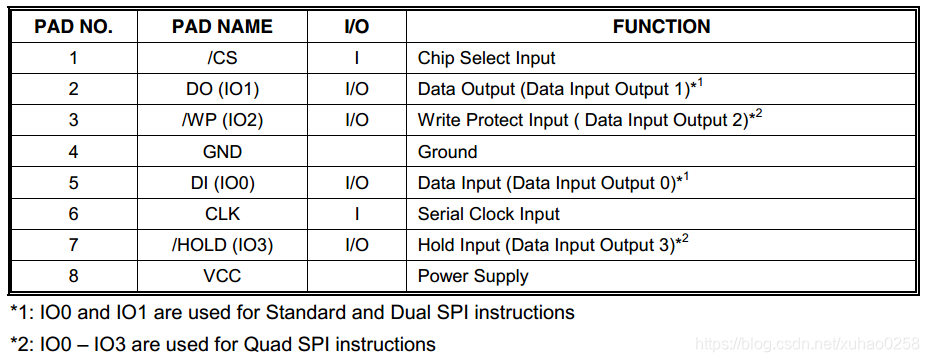

Qual SPI flash 接口:

- Write Project(/WP)

写保护信号的作用是防止 QSPI Flash 的状态寄存器被写入错误的数据,WP 信号低电平有效,但是当状态寄存器 2的 QE 位被置 1 时,WP 信号失去写保护功能,它变成 Quad SPI 的一个双向数据传输信号。

- HOLD(/HOLD)

HOLD 信号的作用是暂停 QSPI Flash 的操作。当 HOLD 信号为低,并且 CS 也为低(选中)时,串行输出信号 DO 将处于高阻态,串行输入信号 DI 与串行时钟信号 SCLK 将被 QSPI Flash 忽略。当 HOLD 拉高以后,QSPI Flash 的读写操作能继续进行。当多个 SPI 设备共享同一组 SPI 总线相同的信号的时候,可以通过 HOLD 来切换信号的流向(相当于 CS 无法区分时用 HOLD 当第二个 CS)。和 WP 信号一样,当状态寄存器 2的 QE 位被置 1 时,HOLD 信号失去保持功能,它也变成 Quad SPI 的一个双向数据传输信号。

将数据写入 SPI NOR 设备的方式因存储芯片是否配备 cache 而异。如果串行 FLASH 是有缓冲的,则可以将页面读入缓冲区,修改并写回芯片。如果 SPI NOR 器件没有缓冲,则必须从外部读取、修改整个页面并将其写回芯片。因此,缓冲 SPI NOR 往往比同类非缓冲 flash 具有更好的写入性能。

NAND FLASH

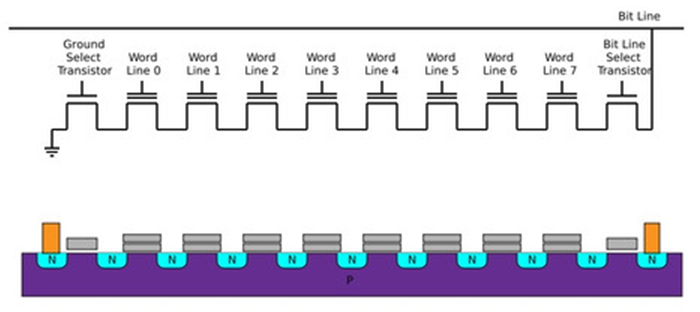

按本图所示,NAND FLASH 中,cell 之间为串联,一个 cell 的源极连接下一个 cell 的漏极:

剖面图:

对某个 cell 进行操作时,不能像 NOR Flash 一样仅为该 word line 施加电压,因为 bit line 连接的 cell 是串联的,而 cell 在 word line 未施加电压的情况下是无法导通的,如果同组的其他 word line 施加电压,该 bit line 中的电流是无法流过的。

为了让 bit line 电流流过,必须为 bit line 连接的所有 cell 对应的 word line 施加一个“导通电压”(一般不会很高,即使这些 word line 上的 cell 实际上无需被操作),并为需要操作的 word line 施加一个“操作电压”(操作电压大小取决于是读取还是编程)。也就是说对一个 cell 的操作需要 word line 和 bit line 上所有的 cell 进行配合,所以对 NAND Flash 的操作(除了擦除)一般是以一个 page 为单位的。

特点:

- 基本存储单元的串联结构减少了金属导线占用的面积,Die 的利用率很高,因此 NAND FLASH 存储密度高,适用于需要大容量存储的应用场合,即适用于 data-storage。

- 基本存储单元的串联结构决定了 NAND FLASH 一般是按照 Page 为单位进行操作的,无法对单个存储单元进行独立寻址,因此程序不可以直接在 NAND 中运行,因此 NAND 是以 Page 为读取单位和写入单位,以 Block 为擦除单位。

- NAND FLASH 写入采用 F-N 隧道效应方式,效率较高,因此 NAND 擦除/写入速率很高,适用于频繁擦除/写入场合。同时 NAND 是以 Page 为单位进行读取的,因此读取速率也不算低(稍低于 NOR)。

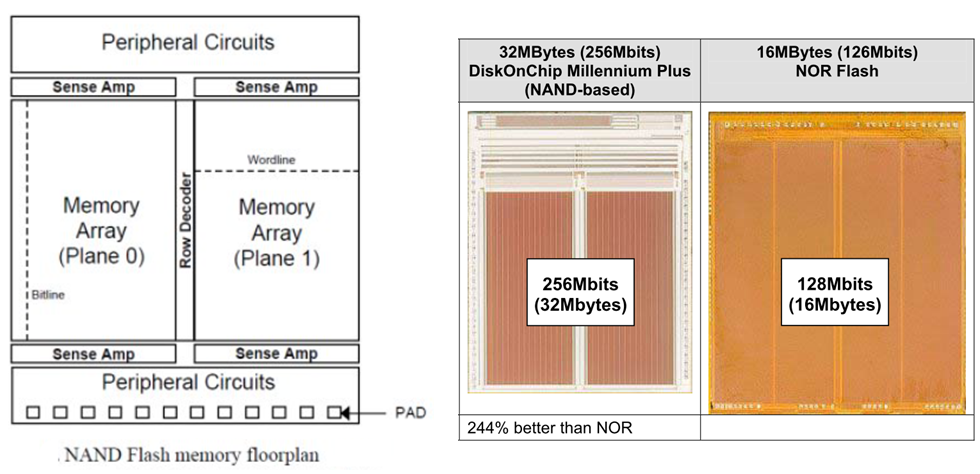

NOR Flash(16MB) 和 NAND Flash(32MB) 占用 die 面积对比:

位交扰(bit disturb)

位交扰(bit disturb)问题是 NAND Flash 中的一种常见现象,指的是在写入、擦除或读取某些存储单元(通常称为“目标单元”)时,附近未被选择的存储单元的状态意外发生改变的现象。这种问题主要由于 NAND Flash 的存储单元排列紧密、工作电压高且存储单元之间的电气耦合效应而产生。

栅极干扰(Gate-disturb): 指的是与正在编程的 cell 连接到同一字线(word line)的那些 cell 产生的非预期的操作。这种干扰在编程时才存在,所以也成为编程干扰 (Programming Disturbs),不过读取时也有可能发生,不过读取电压远小于编程电压,可以忽略不计。

- 发生在未编程或已擦除单元(浮栅无电子)中。这些单元具有较低的单元阈值电压(cell threshold voltage)(之前《读取》一节提到,单元阈值电压可以抵消控制栅极施加的电压,这就是读取 cell 状态的原理)。在编程操作期间,公共字线连接到高电压。穿过隧道氧化物的电场变高,并且可能导致电子从衬底(substrate)穿透到浮置栅极。单元的阈值电压将会增加,并且在严重的情况下单元会被无意地编程(从 1 变 0)。

- 还有可能发生在已编程单元(浮栅有电子)上。这些电子可能从浮栅中逃逸,通过隧穿效应进入控制栅极。

漏极干扰(Drain-disturb)发生在已编程单元(浮栅有电子)中,这些已编程单元与正在编程的单元位于同一位线上(对于热电子注入方式来说,编程时需要为位线(漏极)施加高电压),这些单元将在浮栅和漏极之间经历高电场。这可能导致电子从浮置栅极穿透到漏极(从 0 变 1),并导致单元阈值电压降低。

这些电子的移动可能仅是微量的,不足以改变结果,不过随着操作次数的累积,量变也可能引起质变,发生位翻转的情况。氧化物的缺陷(老化、温度等因素)越大,每次移动的电子就会越多,就越有可能发生位翻转。

因为 NAND Flash 特有的串联位线连接方式,同一个 Page 中未被操作的 cell 也会被附加一个导通电压,虽然正常情况下该电压不足以导致电子穿过绝缘层进入或离开浮栅,但当绝缘层因为多次擦除老化时该情况就很有可能发生。

对比

| 对比项 | NOR | NAND |

|---|---|---|

| 随机读取 | 快 | 慢(寻址慢) |

| 顺序读取 | 快 | 快 |

| 写入速度 | 慢(热电子注入) | 快(F-N 隧穿) |

| 编程功耗 | 大(电流大) | 小 |

| 容量 | 小 | 大(电路简单) |

| 寿命 | 10 万 | 100 万 |

东芝的实际数据:

功耗:对于任何写入密集型应用,NAND 闪存的功耗要低得多。虽然 NOR 闪存和 NAND 闪存的瞬时功率(电压电流)数字看起来不相上下,但 NOR 闪存的总能耗要高得多,因为能耗 = 功率 * 时间。

EEPROM

EEPROM 也属于 FLASH,也是使用浮栅存储电子表示信息,其中有电子为 1,无电子为 0,和上面两种 flash 相反。

不过它可以单独控制一个 WORD(一条 WORD LINE 上的 CELL)的写入,而且无需在写入前进行擦除,也就是说其拥有将 1 修改为 0 和将 0 修改为 1 的双向操作能力。而 NOR/NAND Flash 虽然也可以按 Byte/Page 编程,但不能按 Byte/Page 去除浮栅中的电子(将 0 修改为 1),所以引申出了擦除的概念,必须在编程前对整个 block 进行统一的擦除(许多存储单元共享相同的擦除电路是为了减少电路的复杂性)。

寿命

Flash 的存储单元的寿命取决于其隧穿氧化层(tunnel oxide,浮栅和源漏极间的层),在擦除和编程的过程中,为了让电子通过量子隧穿效应通过该层,需要在其上施加高压电场,这个过程将会对该层带来不可逆的损耗,隧道氧化层在高场应力下的磨损已被发现与正电荷或负电荷的积累有关。对于 NOR Flash 编程时使用的热电子注入方式也会对该层造成损耗。

随着氧化层的损耗,其隔离功能将渐渐丧失,也就是说浮栅内的电子将在没有电场的情况下产生逃逸,造成数据的错误。对于使用了多比特存储单元技术的 flash,损耗严重的氧化层也会导致编程过程无法精确控制注入电子的数量。

Flash 一般都会提供一个表示寿命的指标:P/E cycle(program/erase cycle),表示每个 block 所允许的由一次擦除加上一次编程的循环构成的总次数。

最近的研究表明,在厚度小于 10 纳米的薄氧化层中,高场(high-field)应力(stress)会导致低场漏电流的产生。换句话说,尽管施加的电场较小,但由于之前的高场应力作用,氧化层中仍然会有漏电流流过。

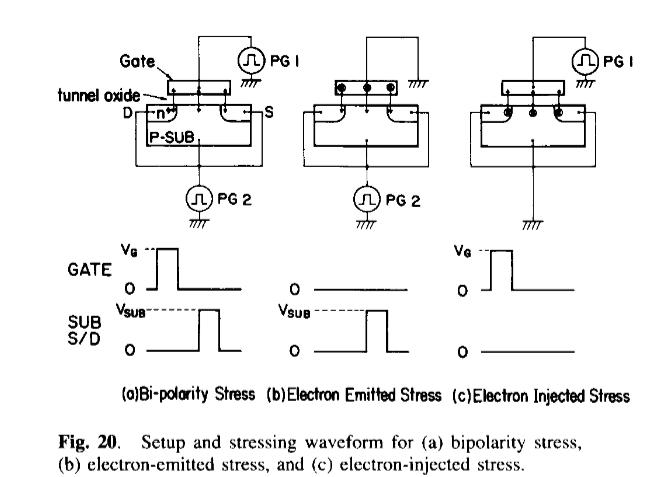

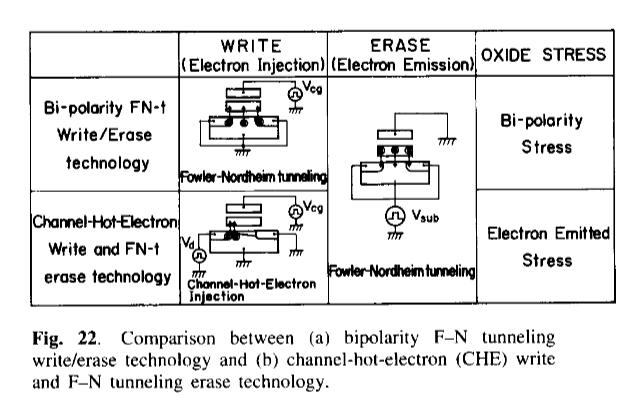

双极性应力与单方向应力的影响

一篇论文《A reliable bi-polarity write/erase technology in flash EEPROMs》研究了双极性高场应力和单方向的高场应力对氧化层寿命的影响。

实验过程:研究人员使用了三种类型的高场动态应力,分别是双极性应力(交替施加正高电压到栅极或衬底/源/漏区域)、电子发射应力(只在衬底/源/漏区域施加正向电压,从栅极发射电子)、以及电子注入应力(只在栅极施加正向电压,从衬底发射电子)。多次重复,观察漏电流大小,漏电流越大说明氧化层磨损越严重。

实验结果:实验表明,双极性应力导致的氧化层漏电流比电子发射和电子注入应力导致的漏电流小一个数量级。这意味着在使用双极性应力时,薄氧化层的退化程度较小,漏电流也较少。

结论:交替的施加正向和反向高电场,可以在一定程度抵消应力的产生,也就是说交替的使用 F-N 隧穿进行电子的发射和注入(擦除和编程)可以减少其磨损。而早期的热电子注入编程无法产生与利用 F-N 隧穿效应的擦除操作相对的反向电场,此举将会加速氧化层的磨损。这也是为什么 NAND Flash 和现代 NOR Flash 采用 F-N 隧穿作为编程方式而不是热电子注入方式的原因。

Macronix 公司给出的实际电压值:

高压与速度

F-N 隧穿效应的速度与电压大小成正比,为了更快进行编程和擦除,一种简单的方法就是提高电压。但电场应力也与电压大小正相关,更高的电压会大大加快氧化层的损耗,这就是一个折中点。

3D Flash 堆叠

为了提高 flash 容量,一种方式是在晶圆的 2D 平面放下更多的 cell,也就必须提升制程精度。但因为物理特性和其他原因限制,制程已经很难继续降低了:

- 隧穿效应增加:随着制程尺寸的减小,存储单元的氧化层变得越来越薄。这使得电子更容易通过隧穿效应(tunneling effect)逃逸出浮置栅极,从而导致数据泄漏或误码率增加。这严重影响了数据的稳定性和存储器的可靠性。

- 短沟道效应(Short Channel Effects):当晶体管尺寸缩小到一定程度后,源极和漏极之间的距离缩短,导致电场增强,使得控制栅极对沟道的控制力减弱。这会引起漏电流增加和器件性能不稳定等问题。

- 成本上升:随着制程技术的缩小,设备成本和制造成本大幅增加。特别是先进的光刻技术(如极紫外光刻 EUV)的引入,极大地提高了工厂的资本支出,使得进一步缩小制程在经济上变得不划算。

- 位交扰问题(Bit Disturb):随着存储单元密度的增加,存储单元之间的电气耦合效应变得更加显著。这会导致在编程或读取某些单元时,未选中单元的电荷状态发生改变,从而增加数据误码率和降低可靠性。

于是出现了 3D 堆叠技术,将 cell 进行垂直堆叠,利用纵向空间提高单位面积存放的 cell 数量,从而提升容量。

晶圆的制造是以单晶硅圆片作为衬底,再往上叠加各种不同层,比如 flash 需要的源极和漏极层、氧化层、浮置栅极层、电极层(电路)等,只要将这些层重复数次并通过硅通孔(TSV , Through-Silicon Via)实现互联就实现了 3D 堆叠。

参考

- NOR FLASH 和 NAND FLASH 基本结构和特点

- NAND 和 NOR Flash 完全学习笔记

- Nand 基本原理

- mosfet 制造工艺,场效应管制造工艺介绍-KIA MOS 管

- What is NOR Flash Memory and How is it Different from NAND?

- 低速接口之 SPI 接口,分类,四种模式,特点

- NAND vs. NOR Flash Memory - Technology Overview

- Why does NAND erase only at block-level and not page level?

- CMOS 模拟电路日记(1) - 信海 - 博客园

- Hot-carrier injection - wikipedia

- Reliability Issues of Flash Memory Cells

- Flash Memory Cells—An Overview

- Program/Erase Cycling Endurance and Data Retention in NOR Flash Memories